# DATA SHEET

# PDI1394L11 1394 AV link layer controller

**Product specification**

1997 Oct 21

### 1394 AV link layer controller

### PDI1394L11

#### 1.0 FEATURES

- IEEE 1394-1995 Standard Link Layer Controller

- Hardware Support for the IEC61883 International Standard of Digital Interface for Consumer Electronics

- Interface to any IEEE 1394-1995 Physical Layer Interface

- 5V Tolerant I/Os

- Single 3.3V supply voltage

### 2.0 DESCRIPTION

The PDI1394L11, Philips Semiconductors 1394 Audio/Video (AV) Link Layer Controller, is an IEEE 1394-1995 compliant link layer controller featuring an embedded AV layer interface. The AV layer is designed to pack and un-pack application data packets for transmission over an IEEE 1394 bus using isochronous data transfers.

The application data is packetized according to the IEC 61883 International Standard of Digital Interface for Consumer Electronic Audio/Video Equipment. The AV layer interface is a byte-wide port capable of accommodating various MPEG-2 and DVC codecs. An 80C51 compatible byte-wide host interface is provided for internal register configuration as well as performing asynchronous data transfers.

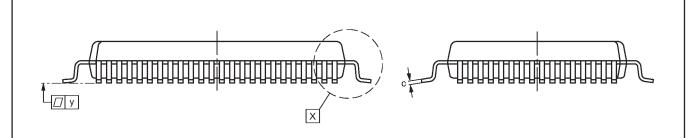

The PDI1394L11 is powered by a single 3.3V power supply and the inputs and outputs are 5V tolerant. It is available in the PQFP80 package.

### 3.0 QUICK REFERENCE DATA

GND = 0V;  $T_{amb} = 25^{\circ}C$

| SYMBOL   | PARAMETER                              | CONDITIONS | MIN    | TYP    | MAX    | UNIT |

|----------|----------------------------------------|------------|--------|--------|--------|------|

| $V_{DD}$ | Functional supply voltage range        |            | 3.0    | 3.3    | 3.6    | V    |

| $I_{DD}$ | Supply current @ V <sub>DD</sub> =3.3V |            |        | 20     |        | mA   |

| SCLK     | Device clock                           |            | 49.147 | 49.152 | 49.157 | MHz  |

#### ORDERING INFORMATION

| PACKAGES              | TEMPERATURE RANGE | OUTSIDE NORTH AMERICA | NORTH AMERICA | PKG. DWG. # |

|-----------------------|-------------------|-----------------------|---------------|-------------|

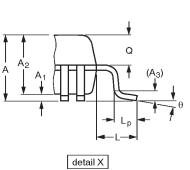

| 80-pin plastic PQFP80 | 0°C to +70°C      | PDI1394L11 BA         | PDI1394L11 BA | SOT318-2    |

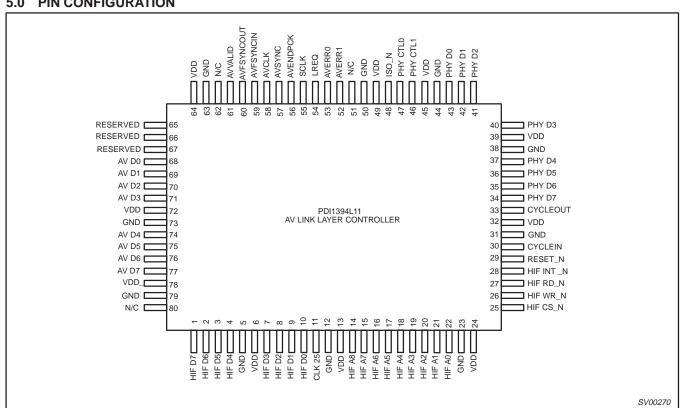

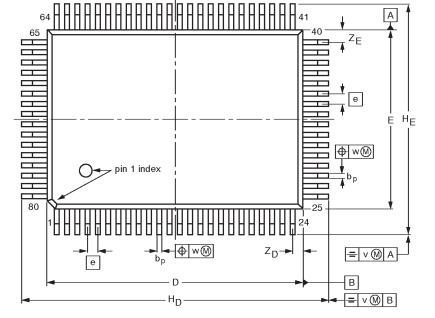

### 5.0 PIN CONFIGURATION

# 1394 AV link layer controller

PDI1394L11

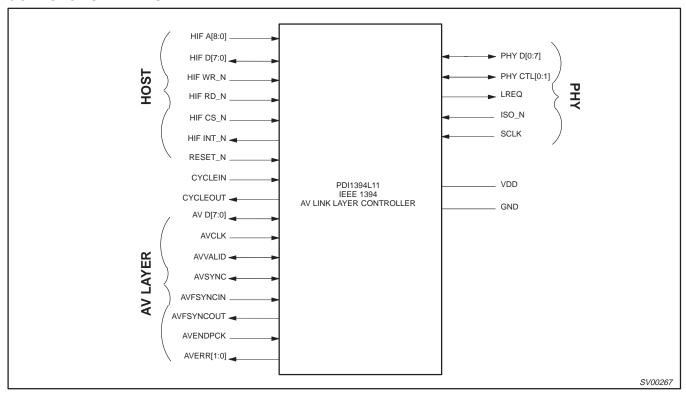

### 6.0 FUNCTIONAL DIAGRAM

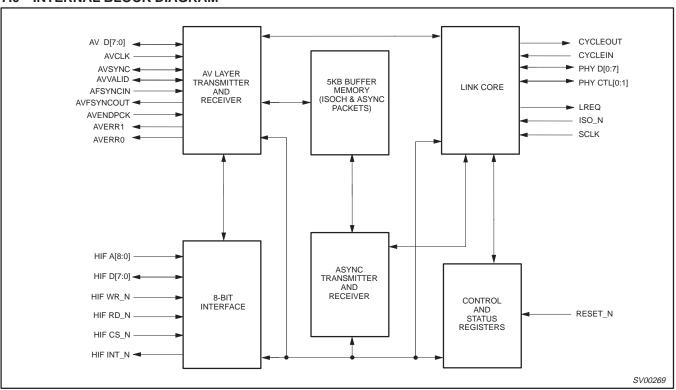

### 7.0 INTERNAL BLOCK DIAGRAM

# 1394 AV link layer controller

PDI1394L11

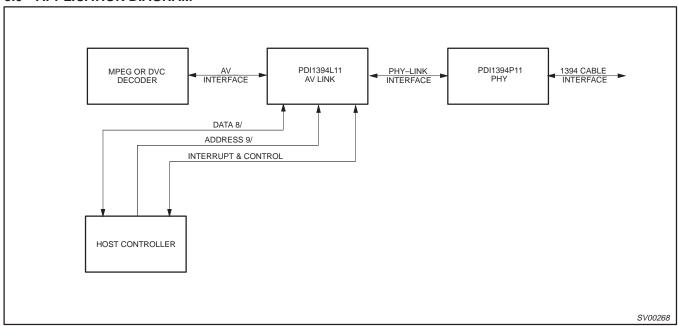

### 8.0 APPLICATION DIAGRAM

### 9.0 PIN DESCRIPTION

### 9.1 Host Interface

| PIN No.                                  | PIN SYMBOL | I/O | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------|------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14, 15, 16, 17,<br>18, 19, 20, 21, 22    | HIF A[8:0] | I   | Host Interface Address 0 through 8. Provides the host with a byte wide interface to internal registers. See description of Host Interface for addressing rules.                                                                                                                                                                                                                                                         |

| 1, 2, 3, 4, 7, 8, 9,<br>10               | HIF D[7:0] | I/O | Host Interface Data 7 (MSB) through 0. Byte wide data path to internal registers.                                                                                                                                                                                                                                                                                                                                       |

| 26                                       | HIF WR_N   | I   | Write enable. When asserted (LOW) in conjunction with HIF CS_N, a write to the PDI1394L11 internal registers is requested. (NOTE: HIF WR_N and HIF RD_N: if these are both LOW in conjunction with HIF CS_N, then a write cycle takes place. This can be used to connect CPUs that use R/W_N line rather than separate RD_N and WR_N lines. In that case, connect the R/W_N line to the HIF WR_N and tie HIF RD_N LOW.) |

| 27                                       | HIF RD_N   | ı   | Read enable. When asserted (LOW) in conjunction with HIF CS_N, a read of the PDI1394L11 internal registers is requested.                                                                                                                                                                                                                                                                                                |

| 25                                       | HIF CS_N   | I   | Chip Select (active LOW). Host bus control signal to enable access to the FIFO and control and status registers.                                                                                                                                                                                                                                                                                                        |

| 28                                       | HIF INT_N  | 0   | Interrupt (active LOW). Indicates a interrupt internal to the PDI1394L11. Read the General Interrupt Register for more information. This pin is open drained and requires a $1K\Omega$ pullup resistor.                                                                                                                                                                                                                 |

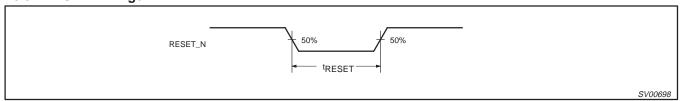

| 29                                       | RESET_N    | I   | Reset (active LOW). The asynchronous master reset to the PDI1394L11.                                                                                                                                                                                                                                                                                                                                                    |

| 6, 13, 24, 32, 39, 45, 49, 64, 72, 78    | $V_{DD}$   |     | $3.3V \pm 0.3V$ power supply                                                                                                                                                                                                                                                                                                                                                                                            |

| 5, 12, 23, 31, 38,<br>44, 50, 63, 73, 79 | GND        |     | Ground reference                                                                                                                                                                                                                                                                                                                                                                                                        |

1997 Oct 21

# 1394 AV link layer controller

PDI1394L11

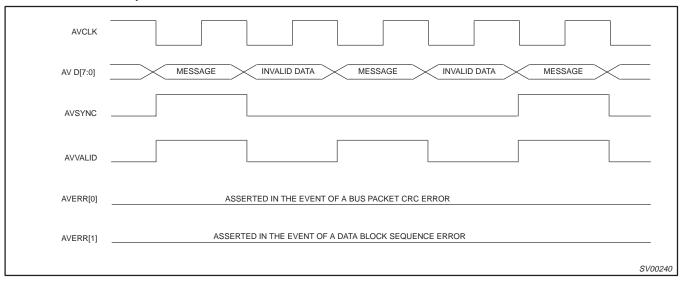

### 9.2 AV Interface

| PIN No.                           | PIN SYMBOL | I/O | NAME AND FUNCTION                                                                                                                                                          |  |

|-----------------------------------|------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 77, 76, 75, 74,<br>71, 70, 69, 68 | AV D[7:0]  | I/O | Audio/Video Data 7 (MSB) through 0. Byte-wide interface to the AV layer.                                                                                                   |  |

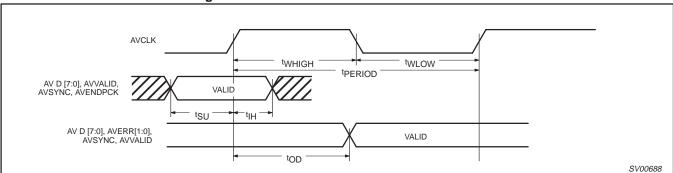

| 58                                | AVCLK      | -   | External application clock. Rising edge active.                                                                                                                            |  |

| 57                                | AVSYNC     | I/O | Start of packet indicator; should only be used when AVVALID is active.                                                                                                     |  |

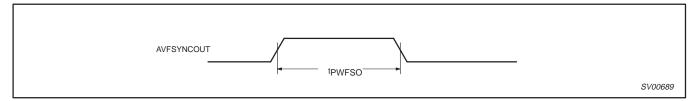

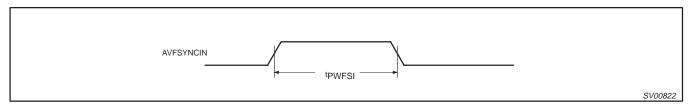

| 59                                | AVFSYNCIN  | I   | Frame sync input. Used for Digital Video (DV). The signal is time stamped and transmitted in the SYT field of ITXHQ2.                                                      |  |

| 60                                | AVFSYNCOUT | 0   | Frame sync output. Signal is derived from SYT field of IRXHQ2.                                                                                                             |  |

| 56                                | AVENDPCK   | I   | End of application packet indication from data source. Required only if input packet is not multiple of 4 bytes. It can be tied LOW for data packets that are 4*N in size. |  |

| 61                                | AVVALID    | I/O | Indicates data on AV D [7:0] is valid                                                                                                                                      |  |

| 53                                | AVERR0     | 0   | CRC error, indicates bus packet containing AV D [7:0] had a CRC error, the current AV packet is unreliable.                                                                |  |

| 52                                | AVERR1     | 0   | Sequence Error. Indicates at least one source packet was lost before the current AV D [7:0]                                                                                |  |

### 9.3 Phy Interface

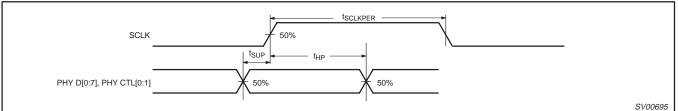

| PIN No.                           | PIN SYMBOL   | I/O | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                |

|-----------------------------------|--------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 34, 35, 36, 37,<br>40, 41, 42, 43 | PHY D[0:7]   | I/O | Data 0 (MSB) through 7 (NOTE: To preserve compatibility to the specified Link-Phy interface of the IEEE 1394–1995 standard, Annex J, bit 0 is the most significant bit). Data is expected on AV D[0:1] for 100Mb/s, AV D[0:3] for 200Mb/s, and AV D[0:7] for 400Mb/s. See IEEE 1394–1995 standard, Annex J for more information. |

| 46, 47                            | PHY CTL[0:1] | I/O | Control Lines between Link and Phy. See 1394 Specification for more information.                                                                                                                                                                                                                                                 |

| 48                                | ISO_N        | I   | Isolation barrier. This terminal is asserted (LOW) when an isolation barrier is present. See IEEE 1394–1995 standard, Annex J for more information (used to request arbitration or read/write PHY registers).                                                                                                                    |

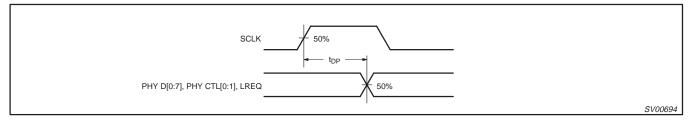

| 54                                | LREQ         | 0   | Link Request. Bus request to access the PHY. See IEEE 1394–1995 standard, Annex J for more information.                                                                                                                                                                                                                          |

| 55                                | SCLK         | ı   | System clock. 49.152MHz input from the PHY (the PHY-LINK interface operates at this frequency).                                                                                                                                                                                                                                  |

### 9.4 Other Pins

| PIN No.    | PIN SYMBOL | I/O | NAME AND FUNCTION                                                                                      |

|------------|------------|-----|--------------------------------------------------------------------------------------------------------|

| 65, 66, 67 | RESERVED   | NA  | These pins are reserved for factory testing. For normal operation they should be connected to ground.  |

| 51, 62, 80 | N/C        | NA  | These are test mode pins and should not be connected or terminated.                                    |

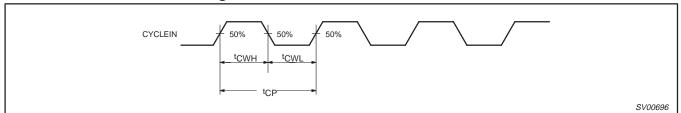

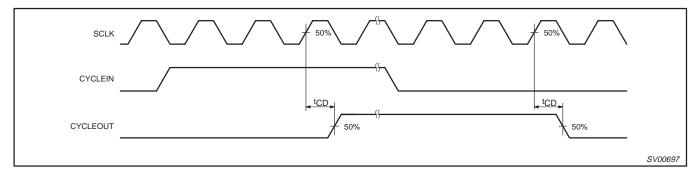

| 30         | CYCLEIN    | I   | Provides the capability to supply an external cycle timer signal for the beginning of 1394 bus cycles. |

| 33         | CYCLEOUT   | 0   | Reproduces the 8kHz cycle clock of the cycle master.                                                   |

| 11         | CLK 25     | 0   | Auxiliary clock, value is SCLK/2 (usually 24.576 MHz)                                                  |

# 1394 AV link layer controller

PDI1394L11

### 10.0 RECOMMENDED OPERATING CONDITIONS

| SYMBOL           | PARAMETER                           | CONDITIONS | LIM    | IITS   | UNIT |

|------------------|-------------------------------------|------------|--------|--------|------|

| STWIBOL          |                                     |            | MIN.   | MAX.   |      |

| V <sub>CC</sub>  | DC supply voltage                   |            | 3.0    | 3.6    | V    |

| VI               | Input voltage                       |            | 0      | 5      | V    |

| V <sub>IH</sub>  | High-level input voltage            |            | 2.0    |        | V    |

| V <sub>IL</sub>  | Low-level input voltage             |            |        | 0.8    | V    |

| I <sub>OH</sub>  | High-level output current           |            |        | 8      | mA   |

| I <sub>OL</sub>  | Low-level output current            |            |        | -8     | mA   |

| dT/dV            | Input transition rise or fall time  |            | 0      | 20     | ns/V |

| T <sub>amb</sub> | Operating ambient temperature range |            | 0      | +70    | °C   |

| SCLK             | System clock                        |            | 49.147 | 49.157 | MHz  |

| AVCLK            | AV interface clock                  |            | 0      | 24     | MHz  |

| t <sub>r</sub>   | Input rise time                     |            |        | 10     | ns   |

| t <sub>f</sub>   | input fall time                     |            |        | 10     | ns   |

### 11.0 ABSOLUTE MAXIMUM RATINGS<sup>1, 2</sup>

In accordance with the Absolute Maximum Rating System (IEC 134). Voltages are referenced to GND (ground = 0V)

| SYMBOL                             | PARAMETER                         | CONDITIONS | LIM  | UNIT                 |      |

|------------------------------------|-----------------------------------|------------|------|----------------------|------|

| STWIBOL                            |                                   | CONDITIONS | MIN  | MAX                  | ONII |

| V <sub>DD</sub>                    | DC supply voltage                 |            | -0.5 | +4.6                 | V    |

| I <sub>IK</sub>                    | DC input diode current            |            | -    | <b>-</b> 50          | mA   |

| VI                                 | DC input voltage                  |            | -0.5 | +5.5                 | V    |

| I <sub>OK</sub>                    | DC output diode current           |            | -    | ±50                  | mA   |

| Vo                                 | DC output voltage                 |            | -0.5 | V <sub>DD</sub> +0.5 | V    |

| I <sub>O</sub>                     | DC output source or sink current  |            | -    | ±50                  | mA   |

| I <sub>GND</sub> , I <sub>CC</sub> | DC V <sub>CC</sub> or GND current |            | -    | ±150                 | mA   |

| T <sub>stg</sub>                   | Storage temperature range         |            | -60  | 150                  | °C   |

| T <sub>amb</sub>                   | Operating ambient temperature     |            | 0    | 70                   | °C   |

| P <sub>tot</sub>                   | Power dissipation per package     |            |      | 0.6                  | W    |

#### NOTES

1997 Oct 21

<sup>1.</sup> Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

The performance capability of a high-performance integrated circuit in conjunction with its thermal environment can create junction temperatures which are detrimental to reliability. The maximum junction temperature of this integrated circuit should not exceed 150°C.

# 1394 AV link layer controller

PDI1394L11

### 11.1 Buffer Memory Sizes

| BUFFER MEMORY                                   | SIZE<br>(Quadlets) |

|-------------------------------------------------|--------------------|

| Asynchronous Receive Transaction Response FIFO  | 64                 |

| Asynchronous Receive Transaction Request FIFO   | 64                 |

| Asynchronous Transmit Transaction Response FIFO | 64                 |

| Asynchronous Transmit Transaction Request FIFO  | 64                 |

| AV Transmit/Receive Buffer                      | 1024               |

### 12.0 FUNCTIONAL DESCRIPTION

### 12.1 Overview

The PDI1394L11 is an IEEE 1394–1995 compliant link layer controller. It provides a direct interface between a 1394 bus and various MPEG–2 and DVC codecs. Via this interface, the AV Link maps and unmaps these AV datastreams from these codecs onto 1394 isochronous bus packets. The AV Link also provides an 8051 compatible microcontroller interface for an attached host controller. Through the host interface port, the host controller can configure the AV layer for transmission or reception of AV datastreams. The host interface port also allows the host controller to transmit and receive 1394 asynchronous data packets.

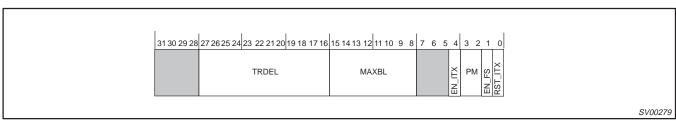

### 12.2 AV interface and AV layer

The AV interface and AV layer allow AV packets to be transmitted from one node to another. The AV transmitter and receiver within the AV layer perform all the functions required to pack and unpack AV packet data for transfer over a 1394 network. Once the AV layer is properly configured for operation, no further host controller service should be required. The operation of the AV layer is half-duplex, i.e., the AV layer can either receive or transmit AV packets at a particular time.

### 12.2.1 The AV Interface

The AV Link provides an 8 bit data path to the AV layer. The 8 bit data path is designed with associated clock and control signals to be compatible with various MPEG–2 and DVC codecs.

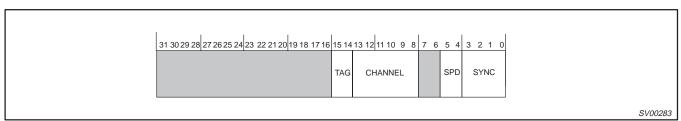

The AV interface port buffer, if so programmed, can time stamp incoming AV packets. The AV packet data is stored in the embedded memory buffer, along with its time stamp information. After the AV packet has been written into the AV layer, the AV layer creates an isochronous bus packet with the appropriate CIP header. The bus packet along with the CIP header is transferred over the appropriate isochronous channel/packet. The size and configuration of isochronous data packet payload transmitted is determined by the AV layer's configuration registers accessible through the host interface.

The AV interface port waits for the assertion for AVVALID and AVSYNC. Note: Do not assert AVSYNC without AVVALID. AVSYNC is aligned with the rising edge of AVCLK and the first byte of data on AVDATA[7:0]. The duration of AVSYNC is one AVCLK cycle. AVSYNC signals the AV layer that the transfer of an AV packet has begun. At the time the AVSYNC is asserted, the AV layer creates a new time stamp in the buffer memory. (This only happens if so configured. The DVC format does not require these time stamps). The time stamp is then transmitted as part of the standard

packet header. This allows the AV receiver to provide the AV packet for output at the appropriate time.

When the DV video is enabled (via the format code of the CIP header), the frame synchronization signal AVFSYNCIN is time stamped and placed in the SYT field. The timestamp value is 3 cycle times (duration of 125µs) in the future and is transmitted in the SYT field of the current CIP header. On the receiver side, when the SYT stamp matches the cycle timer register, a pulse is generated on the AVFSYNCOUT output. The timing for AVFSYNCIN and AVFSYNCOUT are independent of AV clock.

#### 12.2.2 IEC 61883 International Standard

The PDI1394L11 is specifically designed to support the proposed IEC61883 International Standard of Digital Interface for Consumer Electronic Audio/Video Equipment. The IEC specification defines a scheme for mapping various types of AV datastreams onto 1394 isochronous data packets. The standard also defines a software protocol for managing isochronous connections in a 1394 bus called Connection Management Protocol (CMP). It also provides a framework for transfer of functional commands, called Function Control Protocol (FCP).

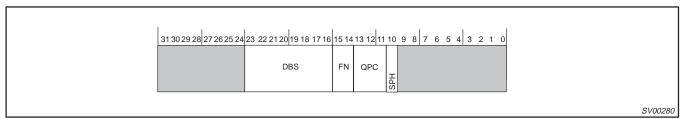

### 12.2.3 CIP Headers

A feature of the IEC61883 International Standard is the definition of Common Isochronous Packet (CIP) headers. These CIP headers contain information about the source and type of datastream mapped onto the isochronous packets.

The AV Layer supports the use of CIP headers. CIP headers are added to transmitted isochronous data packets at the AV data source. When receiving isochronous data packets, the AV layer automatically analyzes their CIP headers. The analysis of the CIP headers determines the method the AV layer uses to unpack the AV data from the isochronous data packets.

The information contained in the CIP headers is accessible via registers in the host interface.

(See IEC61883 International Standard of Digital Interface for Consumer Electronic Audio/Video Equipment for more details on CIP headers).

### 12.3 The host interface

The host interface allows an 8 bit CPU to access all registers and the asynchronous packet queues. It is specifically designed for an 8051 microcontroller but can also be used with other CPUs. There are 64 register addresses (for quadlet wide registers). To access

# 1394 AV link layer controller

PDI1394L11

bytes rather than quadlets the address spaces is 256 bytes, requiring 8 address lines.

The use of an 8 bit interface introduces an inherent problem that must be solved: register fields can be more than 8 bits wide and be used (control) or changed (status) at every internal clock tick. If such a field is accessed through an 8 bit interface it requires more than one read or write cycle, and the value should not change in between to maintain consistency. To overcome this problem accesses to the chip's internal register space are always 32 bits, and the host interface must act as a converter between the internal 32 bit accesses and external 8 bit accesses. This is where the shadow registers come in.

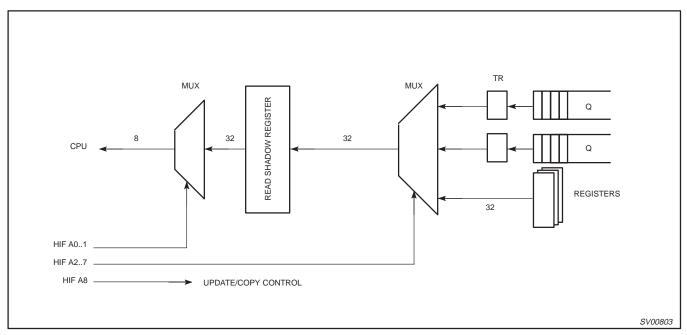

### 12.3.1 Read accesses

To read an internal register the host interface can make a snapshot (copy) of that specific register which is then made available to the CPU 8 bits at a time. The register that holds the snapshot copy of the real register value inside the host interface is called the **read**

**shadow register**. During a read cycle address lines HIF A0 and HIF A1 are used to select which of the 4 bytes currently stored in the **read shadow register** is output onto the CPU data bus. This selection is done by combinatorial logic only, enabling external hardware to toggle these lines through values 0 to 3 while keeping the chip in a read access mode to get all 4 bytes out very fast (in a single extended read cycle), for example into an external quadlet register.

This solution requires a control line to direct the host interface to make a snapshot of an internal register when needed, as well as the internal address of the target register. The register address is connected to input address lines HIF A2..HIF A7, and the update control line to input address line HIF A8. To let the host interface take a new snapshot the target address must be presented on HIF A2..HIF A7 and HIF A8 must be raised while executing a read access. The new value will be stored in the **read shadow register** and the selected byte (HIF A0, HIF A1) appears on the output.

### NOTES:

- 1. It is not required to read all 4 bytes of a register before reading another register. For example, if only byte 2 of register 0x54 is required a read of byte address 0x100 + (0x54) + 2 = 0x156 is sufficient.

- 2. The update control line does not necessarily have to be connected to the CPU address line HIF A8. This input could also be controlled by other means, for example a combinatorial circuit that activates the update control line whenever a read access is done for byte 0. This makes the internal updating automatic for quadlet reading.

3. Reading the bytes of the read shadow register can be done in any order and as often as needed.

1997 Oct 21

# 1394 AV link layer controller

PDI1394L11

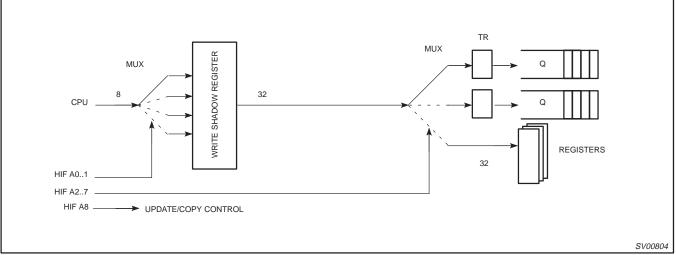

#### 12.3.2 Write accesses

To write to an internal register the host interface must collect the 4 byte values into a 32 bit value and then write the result to the target register in a single clock tick. This requires a register to hold the 32 bit value being compiled until it is ready to be written to the actual target register. This temporary register inside the host interface is called the **write shadow register**. During all write cycles address lines HIF A0 and HIF A1 are used to select which of the 4 bytes of the **write shadow register** is to be written with the value on the CPU data bus. Only one byte can be written in a single write access cycle.

This solution requires a control line to direct the host interface to copy the **write shadow register** to the actual destination register when ready, as well as the internal address of that register. The destination register address is connected to input address lines HIF A2..HIF A7, and the update control line to input address line HIF A8. To let the host interface make the internal transfer the target address must be presented on HIF A2..HIF A7 and HIF A8 must be raised while executing a write access. The current value on the CPU data bus will be stored in the **write shadow register** at the selected byte (HIF A0, HIF A1) and the result will be copied into the specified destination register.

### NOTES:

- 1. It is not required to write all 4 bytes of a register: those bytes that are either reserved (undefined) or don't care do not have to be written in which case they will be assigned the value that was left in the corresponding byte of the **write shadow register** from a previous write access. For example, to acknowledge an interrupt for the isochronous receiver (external address 0x04C), a single byte write to location 0x100+(0x4C)+3 = 0x14F is sufficient. The value 256 represents setting HIF A8=1. The host interface cannot directly access the FIFOs, but instead reads from/writes into a transfer register (shown as TR in the Figures above). Data is moved between FIFO and TR by internal logic as soon as possible without CPU intervention.

- 2. The update control line does not necessarily have to be connected to the CPU address line HIF A8. This input could also be controlled by other means, for example a combinatorial circuit that activates the update control line whenever a write access is done for byte 3. This makes the internal updating automatic for quadlet writing.

- 3. Writing the bytes of the read shadow register can be done in any order and as often as needed (new writes simply overwrite the old value).

1997 Oct 21

### 1394 AV link layer controller

PDI1394L11

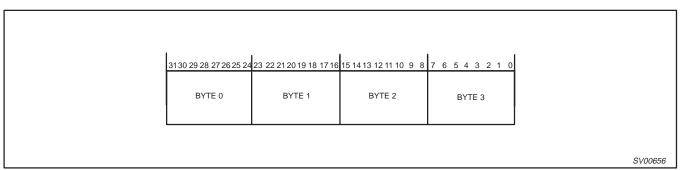

### 12.3.3 Byte order

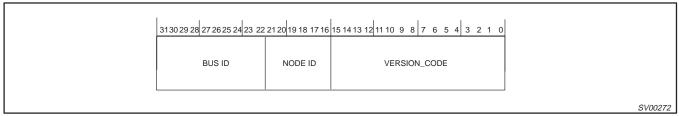

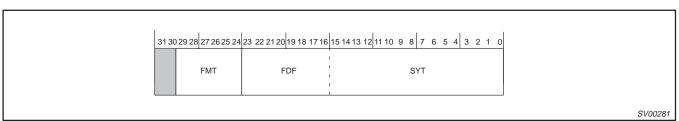

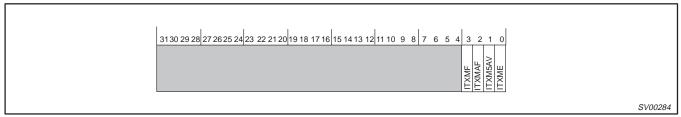

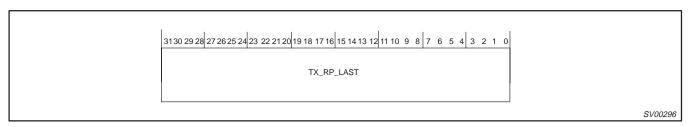

The bytes in each quadlet are numbered 0..3 from left (most significant) to right (least significant) as shown in Figure 1. To access a register at internal address N the CPU should use addresses E:

$E=4\ N$  ; to access the upper 8 bits of the register.  $E=4\ N+1$  ; to access the upper middle 8 bits of the register.  $E=4\ N+2$  ; to access the lower middle 8 bits of the register.  $E=4\ N+3$  ; to access the lower 8 bits of the register.

#### 12.3.4 Accessing the packet queues

Although entire incoming packets are stored in the receiver buffer memory they are not randomly accessible. These buffers act like fifos and only the frontmost (oldest) data quadlet entry is accessible for reading. Therefore only one location (register address) is allocated to each of the two receiver queues. Reading this location returns the head entry of the queue, and at the same time removes it from the queue, making the next stored data quadlet accessible.

With the current host interface such a read is in fact a move operation of the data quadlet from the queue to the read shadow

register. Once the data is copied into the read shadow register it is no longer available in the queue itself so the CPU should always read all 4 bytes before attempting any other read access (be careful with interrupt handlers for AVLink!).

A similar argument applies to the transmitter queues. Data cannot be written arbitrarily, but only to the next available free location. Since the transmitter needs to know when the packet is complete (all data stored in memory, so that it may start the arbitration process on the 1394 bus) two separate register locations are reserved per transmitter queue: one to write all but the last packet quadlet to, and one to write the last quadlet of every packet to. Writing to any of these register locations stores the data in the queue and makes the next memory location accessible for writing.

#### NOTE:

Because of the way it is implemented memory access is not always immediate; consequently it may take some time before the next data quadlet in the queue is accessible after reading or writing the current one. Status flags are provided to the CPU to indicate availability.

Figure 1. Byte order in quadlets as implemented in the host interface

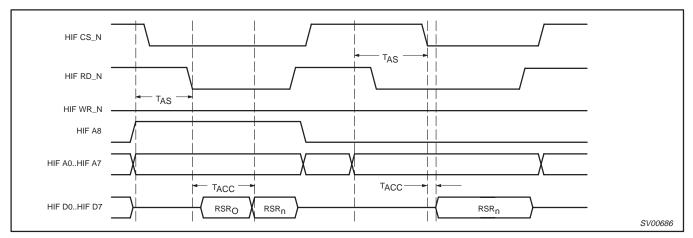

### 12.3.5 The CPU bus interface signals

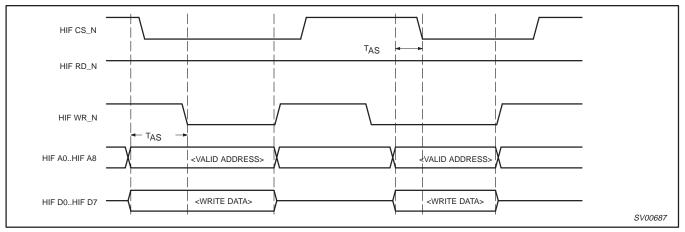

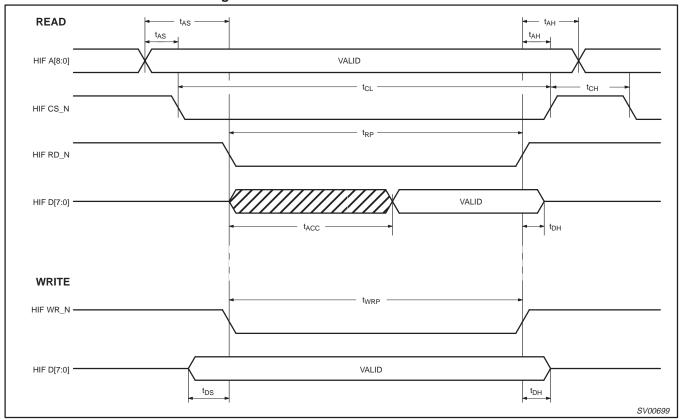

The CPU interface is directly compatible with an 8051 microcontroller. It uses a separate HIF RD\_N and HIF WR\_N inputs and a HIF CS\_N chip select line, all of which are active LOW. There are 9 address inputs (HIF A0..HIF A8) and 8 data in/out lines HIF D0..HIF D7. An open drain HIF INT\_N output is used to signal interrupts to the CPU.

The CPU is not required to run at a clock that is synchronous to the 1394 base clock. The control signals will be resampled by the host interface before being used internally.

An access through the host interface starts when HIF  $CS_N = 0$  and either HIF  $WR_N = 0$  or HIF  $RD_N = 0$ . Typically the chip select signal is derived from the upper address lines of the CPU (address decode stage), but it could also be connected to a port pin of the CPU to avoid the need for an external address decoder in very simple CPU systems. When both HIF  $CS_N = 0$  and HIF  $RD_N = 0$  the host interface will start a read access cycle, so the cycle is triggered at the falling edge of either HIF  $CS_N = 0$  or HIF  $RD_N = 0$ , whichever is later.

Very shortly after the start of the cycle, the selected byte in the read shadow register will be output (indicated in Figure 2 as  $RSR_O$ ). If HIF A8 is asserted then the target register value will be copied into the read shadow register, leading to a new value  $RSR_n$  some time later in the read cycle. If HIF A8 is LOW, then the read shadow register will not change.

A write access starts when the later of HIF CS\_N and HIF WR\_N becomes LOW (see Figure 3). Data is written to the shadow register, following which, if HIF A8 is asserted, the shadow register value is copied to the addressed register.

### NOTES:

- The time between the end of any access and the start of the next access must be at least t<sub>CH</sub> which needs to be greater than (2 x SCLK).

- 2. When HIF A8 = 0 for either write or read access the address bits HIF A2..HIF A7 are ignored.

- 3. If both HIF WR\_N = 0 and HIF RD\_N = 0 while HIF CS\_N = 0, then a write cycle takes place.

### 1394 AV link layer controller

PDI1394L11

Figure 2. Read cycle signal timing (2 independent read cycles)

Figure 3. Write cycle signal timing (2 independent write cycles)

### 12.4 The Asynchronous Packet Interface

The PDI1394L11 provides an interface to asynchronous data packets through the registers in the host interface. The format of the asynchronous packets is specified in the following sections.

### 12.4.1 Reading an Asynchronous Packet

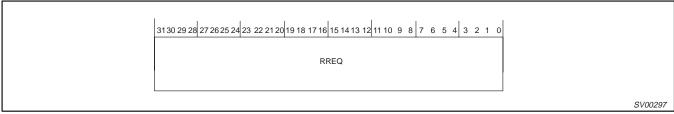

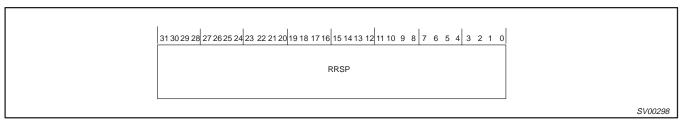

Upon reception of a packet, the packet data is stored in the appropriate receive FIFO, either the Request or Response FIFO. The location of the packet is indicated by either the RREQQQAV or RRSPQAV status bit being set in the Asynchronous Interrupt Acknowledge (ASYINTACK) register. The packet is transferred out of the FIFO by successive reads of the Asynchronous Receive Request (RREQ) or Asynchronous Receive Response (RRSP) register. The end of the packet (the last quadlet) is indicated by either the RREQQLASTQ or RRSPQLASTQ bit set in ASYINTACK. Attempting to read the FIFO when either RREQQQAV bit or RRSPQQAV bit is set to 0 (in the Asynchronous RX/TX interrupt acknowledge (ASYINTACK) register) will result in a queue read error.

### 12.4.2 Writing an Asynchronous Packet

An asynchronous packet intended for transmission is first stored in the appropriate Transmitter FIFO. Once writing to the FIFO is complete, the link layer controller arbitrates for the bus to transmit the packet.

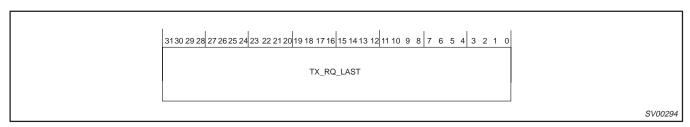

To generate an asynchronous packet, the first and next to last quadlets of the packet must be written to the Asynchronous Transmit Request Next (TX\_RQ\_NEXT) register, for request type packets, or the Asynchronous Transmit Response Next (TX\_RP\_NEXT) register, for response type packets. The last quadlet of the packet is written to the Asynchronous Transmit Request Last (TX\_RQ\_LAST) register, for request type packets, or the Asynchronous Transmit Response Last (TX\_RP\_LAST) register, for response type packets. After writing the last quadlet, the packet is automatically queued by the AVlink layer controller for transmission over the bus.

1997 Oct 21

# 1394 AV link layer controller

PDI1394L11

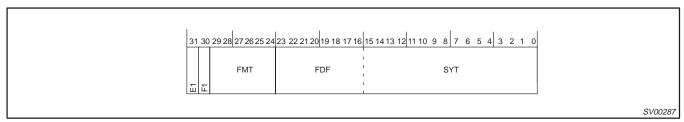

#### 12.5 Link Packet Data Formats

The data formats for transmission and reception of data are shown below. The transmit format describes the expected organization for data presented to the link at the asynchronous transmit, physical response, or isochronous transmit FIFO interfaces.

### 12.5.1 Asynchronous Transmit Packet Formats

These sections describe the formats in which packets need to be delivered to the queues (FIFOs) for transmission. There are four basic formats as follows:

| ITEM | FORMAT               | USAGE                              | TRANSACTION<br>CODE<br>(tCode) |

|------|----------------------|------------------------------------|--------------------------------|

| 1    | No poskot data       | Quadlet read requests              | 4                              |

|      | No-packet data       | Quadlet/block write responses      | 2                              |

|      |                      | Qaudlet write requests             | 0                              |

| 2    | Quadlet packet       | Quadlet read responses             | 6                              |

|      |                      | Block read requests                | 5                              |

|      |                      | Block write requests               | 1                              |

| 3    | Block Packet         | Block read responses               | 7                              |

|      |                      | Lock requests                      | 9                              |

|      |                      | Lock responses                     | B <sub>hex</sub>               |

| 4    | Unformatted transmit | Concatenated self-ID / PHY packets | E <sub>hex</sub>               |

Each packet format uses several fields (see names and descriptions below). More information about these fields (not the format) can be found in the 1394 specification. Grey fields are reserved and should be set to zero values.

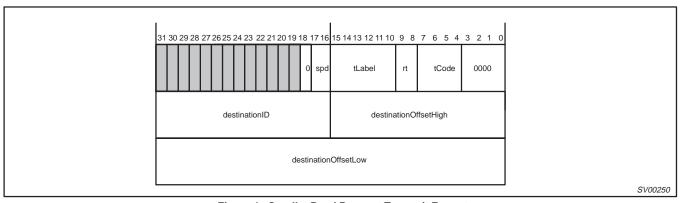

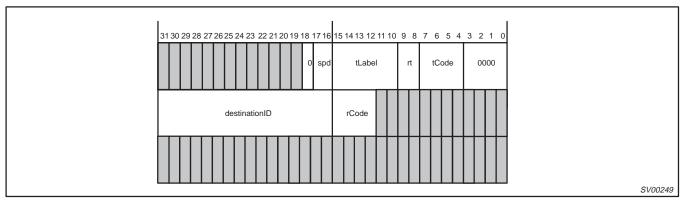

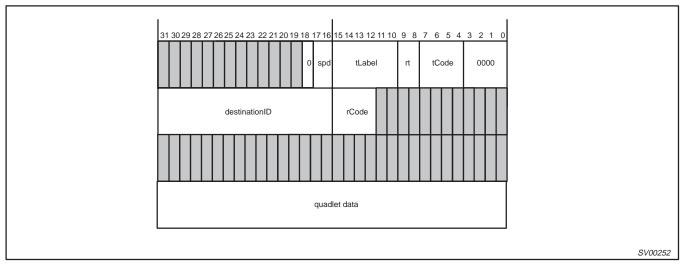

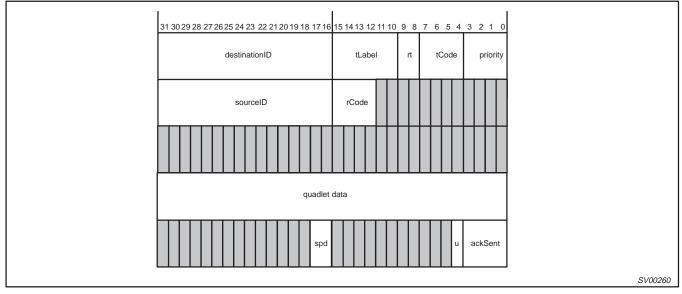

### 12.5.1.1 No-data Transmit

The no-data transmit formats are shown in Figures 4 and 5. The first quadlet contains packet control information. The second and third quadlets contain 16-bit destination ID and either the 48-bit, quadlet aligned destination offset (for requests) or the response code (for responses).

Figure 4. Quadlet Read Request Transmit Format

# 1394 AV link layer controller

PDI1394L11

Figure 5. Quadlet/Block Write Response Packet Transmit Format

**Table 1. No-Data Transmit Format**

| Field Name                                    | Description                                                                                                               |  |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|

| spd                                           | This field indicates the speed at which this packet is to be sent. 00=100 Mbs, 01=200 Mbs, and 10=400 Mbs. 11 = undefined |  |

| tLabel                                        | This field is the transaction label, which is used to pair up a response packet with its corresponding request packet.    |  |

| rt                                            | The retry code for this packet. Supported values are: 00=retry1, and 01=retryX.                                           |  |

| tCode                                         | The transaction code for this packet.                                                                                     |  |

| DestinationID                                 | Contains a node ID value.                                                                                                 |  |

| DestinationOffsetHigh<br>DestinationOffsetLow | The concatenation of these two field addresses a quadlet in the destination node's address space.                         |  |

| rCode                                         | Response code for write response packet.                                                                                  |  |

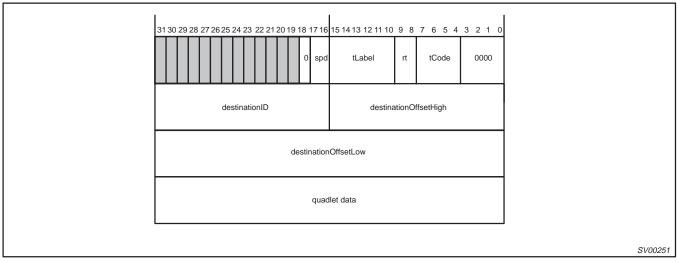

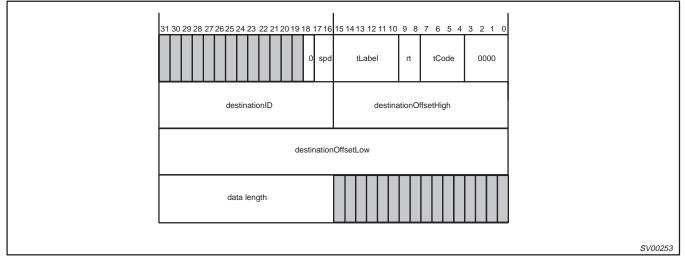

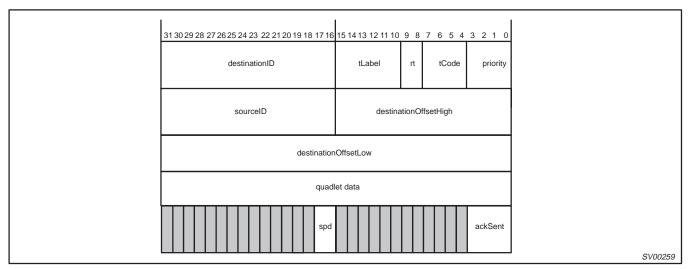

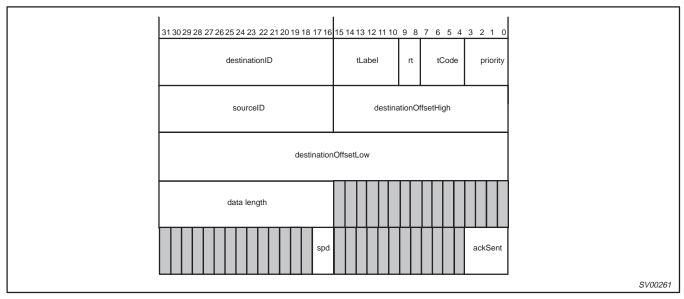

### 12.5.1.2 Quadlet Transmit

Three quadlet transmit formats are shown below. In these figures: The first quadlet contains packet control information. The second and third quadlets contain 16-bit destination ID and either the 48-bit quadlet-aligned destination offset (for requests) or the response code (for responses).

The fourth quadlet contains the quadlet data for read response and write quadlet request formats, or the upper 16 bits contain the data length for the block read request format.

Figure 6. Quadlet Write Request Transmit Format

# 1394 AV link layer controller

PDI1394L11

Figure 7. Quadlet Read Response Transmit Format

Figure 8. Block Read Request Transmit Format

### **Table 2. Quadlet Transmit Fields**

| Field Name                                                                                | Description                                                                                        |

|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| spd, tLabel, rt, tCode, destinationID, destinationOffsetHigh, destinationOffsetLow, rCode | See Table 1.                                                                                       |

| Quadlet data                                                                              | For quadlet write requests and quadlet read responses, this field holds the data to be transferred |

| Data length                                                                               | The number of bytes requested in a block read request                                              |

# 1394 AV link layer controller

PDI1394L11

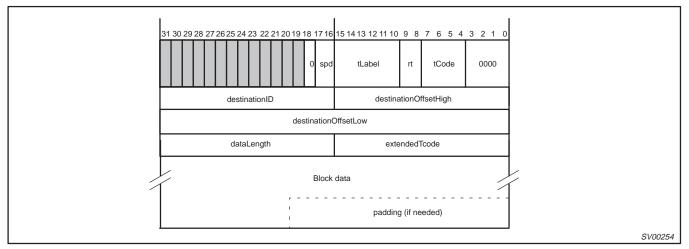

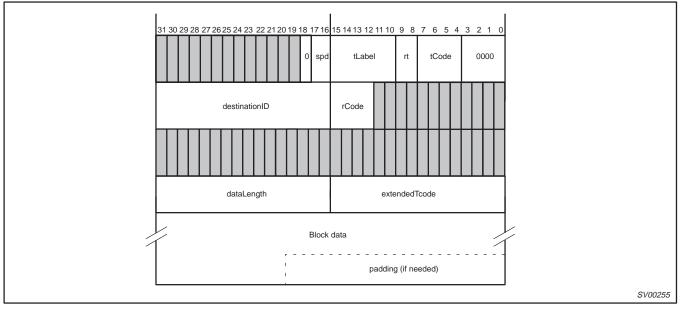

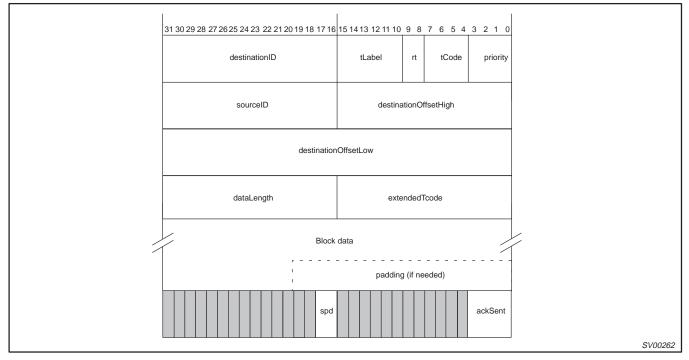

#### 12.5.1.3 Block Transmit

The block transmit format is shown below, this is the generic format for reads and writes. The first quadlet contains packet control information. The second and third quadlets contain the 16-bit destination node ID and either the 48-bit destination offset (for requests) or the response code and reserved data (for responses). The fourth quadlet contains the length of the data field and the extended transaction code (all zeros except for lock transaction). The block data, if any, follows the extended transaction code.

Figure 9. Block Packet Transmit Format

Figure 10. Block Read or Lock Response Transmit Format

# 1394 AV link layer controller

PDI1394L11

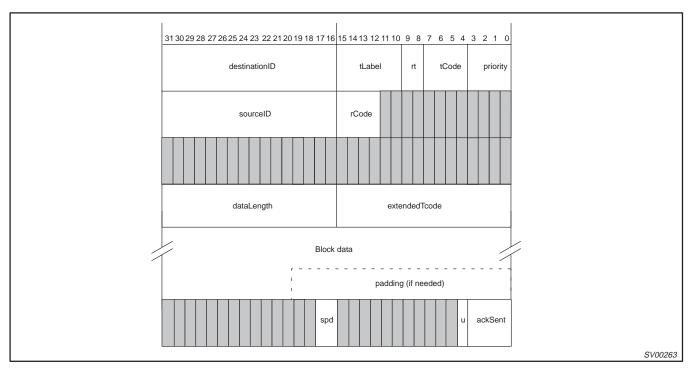

Table 3. Block Transmit Field

| Field Name                                                                                | Description                                                                                                                                                                                                                                       |  |  |

|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| spd, tLabel, rt, tCode, destinationID, destinationOffsetHigh, destinationOffsetLow, rCode | See Table 2.                                                                                                                                                                                                                                      |  |  |

| dataLength                                                                                | The number of bytes of data to be transmitted in this packet                                                                                                                                                                                      |  |  |

| extendedTcode                                                                             | The tCode indicates a lock transaction, this specifies the actual lock action to be performed with the data in this packet.                                                                                                                       |  |  |

| block data                                                                                | The data to be sent. If dataLength=0, no data should be written into the FIFO for this field. Regardless of the destination or source alignment of the data, the first byte of the block must appear in the high order byte of the first quadlet. |  |  |

| padding                                                                                   | If the dataLength mod 4 is not zero, then zero–value bytes are added onto the end of the packet to guarantee that a whole number of quadlets is sent.                                                                                             |  |  |

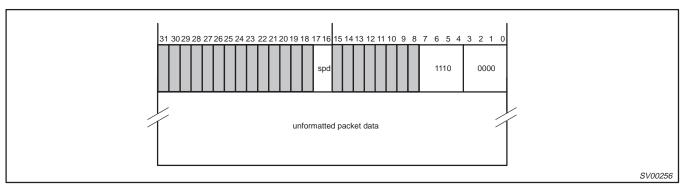

### 12.5.1.4 Unformatted Transmit

The unformatted transmit format is shown in Figure 11. The first quadlet contains packet control information. The remaining quadlets contain data that is transmitted without any formatting on the bus. No CRC is appended on the packet, nor is any data in the first quadlet sent. This is used to send PHY configuration and Link-on packets. Note that the bit-inverted check quadlet must be included in the FIFO since the AV Link core will not generate it.

Figure 11. Unformatted Transmit Format

### 12.5.2 Asynchronous Receive Packet Formats

This section describes the asynchronous receive packet formats. Four basic asynchronous data packet formats and one confirmation format exist:

**Table 4. Asynchronous Data Packet Formats**

| ITEM | FORMAT               | USAGE                               | TRANSACTION CODE |

|------|----------------------|-------------------------------------|------------------|

| 4    | No poekat data       | Quadlet read requests               | 4                |

| '    | No-packet data       | Quadlet/block write responses       | 2                |

| 2    | Quadlat packat       | Qaudlet write requests              | 0                |

| 2    | Quadlet packet       | Quadlet read responses              | 6                |

|      |                      | Block read requests                 | 5                |

|      | Block Packet         | Block write requests                | 1                |

| 3    |                      | Block read responses                | 7                |

|      |                      | Lock requests                       | 9                |

|      |                      | Lock responses                      | B <sub>hex</sub> |

| 4    | Self-ID / PHY packet | Concatenated self-ID / PHY packets  | E <sub>hex</sub> |

| 5    | Confirmation packet  | Confirmation of packet transmission | 8                |

Each packet format uses several fields. More information about most of these fields can be found in the 1394 specification.

# 1394 AV link layer controller

PDI1394L11

Table 5. Asynchronous Receive Fields

| Field Name                                     | Description                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| destinationID                                  | This field is the concatenation of busNumbers (or all ones for "local bus") and nodeNumbers (or all ones for broadcast) for this node.                                                                                                                                                                                                                                                       |

| tLabel                                         | This field is the transaction label, which is used to pair up a response packet with its corresponding request packet.                                                                                                                                                                                                                                                                       |

| rt                                             | The retry code for this packet. 00=retry1, 01=retryX, 10=retryA, 11=retryB.                                                                                                                                                                                                                                                                                                                  |

| tCode                                          | The transaction code for this packet.                                                                                                                                                                                                                                                                                                                                                        |

| priority                                       | The priority level for this packet (0000 for cable environment).                                                                                                                                                                                                                                                                                                                             |

| sourceID                                       | This is the node ID of the sender of this packet.                                                                                                                                                                                                                                                                                                                                            |

| destinationOffsetHigh,<br>destinationOffsetLow | The concatenation of these two field addresses a quadlet in this node's address space.                                                                                                                                                                                                                                                                                                       |

| rCode                                          | Response code for response packets.                                                                                                                                                                                                                                                                                                                                                          |

| quadlet data                                   | For quadlet write requests and quadlet read responses, this field holds the data received.                                                                                                                                                                                                                                                                                                   |

| dataLength                                     | The number of bytes of data to be received in a block packet.                                                                                                                                                                                                                                                                                                                                |

| extendedTcode                                  | If the tCode indicates a lock transaction, this specifies the actual lock action to be performed with the data in this packet.                                                                                                                                                                                                                                                               |

| block data                                     | The data received. If dataLength=0, no data will be written into the FIFO for this field. Regardless of the destination or source alignment of the data, the first byte of the block will appear in the high order byte of the first quadlet.                                                                                                                                                |

| padding                                        | If the dataLength mod 4 is not zero, then zero-value bytes are added onto the end of the packet to guarantee that a whole number of quadlets is sent.                                                                                                                                                                                                                                        |

| u                                              | Unsolicited response tag bit. This bit is set to one (1) if the received response was unsolicited.                                                                                                                                                                                                                                                                                           |

| ackSent                                        | This field contains the acknowledge code that the link layer returned to the sender of the received packet. For packets that do not need to be acknowledged (such as broadcasts) the field contains the acknowledge value that would have been sent if an acknowledge had been required. The values for this field are listed in Table 6 (they also can be found in the IEEE 1394 standard). |

### Table 6. Acknowledge codes

| Code                                    | Name           | Description                                                                                                                                                                                                                                                                                 |

|-----------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0001                                    | ack_complete   | The node has successfully accepted the packet. If the packet was a request subaction, the destination node has successfully completed the transaction and no response subaction shall follow.                                                                                               |

| 0010                                    | ack_pending    | The node has successfully accepted the packet. If the packet was a request subaction, a response subaction will follow at a later time. This code shall not be returned for a response subaction.                                                                                           |

| 0100                                    | ack_busy_X     | The packet could not be accepted. The destination transaction layer may accept the packet on a retry of the subaction.                                                                                                                                                                      |

| 0101                                    | ack_busy_A     | The packet could not be accepted. The destination transaction layer will accept the packet when the node is not busy during the next occurrence of retry phase A.                                                                                                                           |

| 0110                                    | ack_busy_B     | The packet could not be accepted. The destination transaction layer will accept the packet when the node is not busy during the next occurrence of retry phase B.                                                                                                                           |

| 1101                                    | ack_data_error | The node could not accept the block packet because the data field failed the CRC check, or because the length of the data block payload did not match the length contained in the dataLength field. This code shall not be returned for any packet that does not have a data block payload. |

| 1110                                    | ack_type_error | A field in the request packet header was set to an unsupported or incorrect value, or an invalid transaction was attempted (e.g., a write to a read-only address).                                                                                                                          |

| 0000, 0011,<br>0111 – 1100,<br>and 1111 | reserved       |                                                                                                                                                                                                                                                                                             |

# 1394 AV link layer controller

PDI1394L11

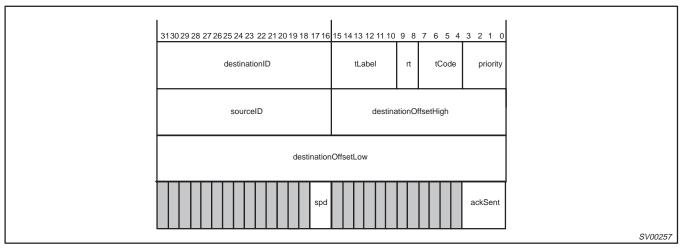

#### 12.5.2.1 No-Data Receive

The no-data receive formats are shown below. The first quadlet contains the destination node ID and the rest of the packet header. The second and third quadlet contain 16-bit source ID and either the 48-bit, quadlet-aligned destination offset (for requests) or the response code (for responses). The last quadlet contains packet reception status.

Figure 12. Quadlet Read Request Receive Format

Figure 13. Write Response Receive Format

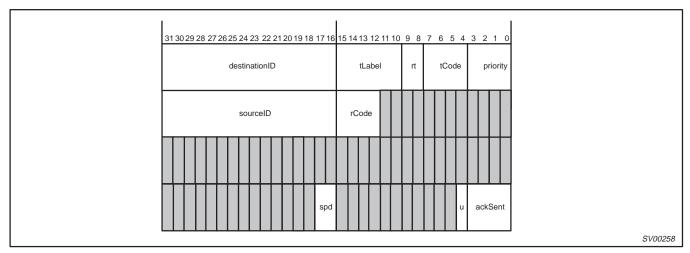

#### 12.5.2.2 Quadlet Receive

The quadlet receive formats are shown below. The first quadlet contains the destination node ID and the rest of the packet header. The second and third quadlets contain 16-bit source ID and either the 48-bit, quadlet-aligned destination offset (for requests) or the response code (for responses). The fourth quadlet is the quadlet data for read responses and write quadlet requests, and is the data length and reserved for block read requests. The last quadlet contains packet reception status.

# 1394 AV link layer controller

PDI1394L11

Figure 14. Quadlet Write Request Receive Format

Figure 15. Quadlet Read Response Receive Format

# 1394 AV link layer controller

PDI1394L11

Figure 16. Block Read Request Receive Format

### 12.5.2.3 Block receive

The block receive format is shown below. The first quadlet contains the destination node ID and the rest of the packet header. The second and third quadlets contain 16-bit sourceID and either the 48-bit destination offset (for requests) or the response code and reserved data (for responses). The fourth quadlet contains the length of the data field and the extended transaction code (all zeros except for lock transactions). The block data, if any, follows the extended code. The last quadlet contains packet reception status.

Figure 17. Block Write or Lock Request Receive Format

# 1394 AV link layer controller

PDI1394L11

Figure 18. Block Read or Lock Response Receive Format

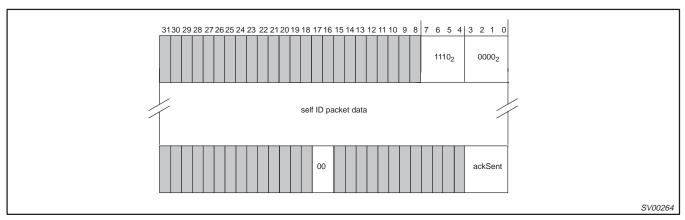

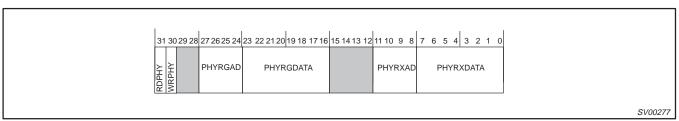

### 12.5.2.4 Self-ID and PHY packets receive

The self-ID and PHY packet receive formats are shown below. The first quadlet contains a synthesized packet header with a tCode of 0xE (hex). For self-ID information, the remaining quadlets contain data that is received from the time a bus reset ends to the first subaction gap. This is the concatenation of all the self-ID packets received. Note that the bit-inverted check quadlet is included in the Read Request FIFO and the application must check it.

Figure 19. Self-ID Receive Format

The "ackSent" field will either be "ACK\_DATA\_ERROR" if a non-quadlet-aligned packet is received or there was a data overrun, or "ACK\_COMPLETE" if the entire string of self-ID packets was received.

### 1394 AV link layer controller

PDI1394L11

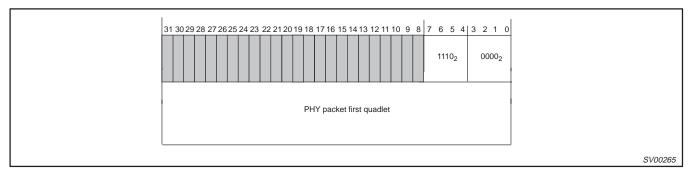

Figure 20. PHY Packet Receive Format

For PHY packets, there is a single following quadlet which is the first quadlet of the PHY packet. The check quadlet has already been verified and is not included.

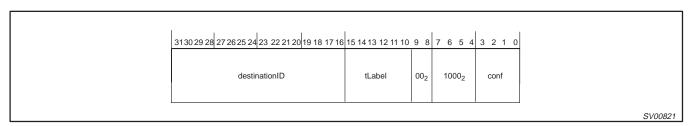

#### 12.5.2.5 Transaction data confirmation formats

After a packet from one of the queues has been transmitted, the asynchronous transmitter assembles a confirmation (see Figure 21) which is used to confirm the result of the transmission to the higher layers. Separate confirmations are assembled for request and response transmissions. Request confirmations are written into the request queue and response confirmations are written into the response queue.

Figure 21. Request and response confirmation format

### Table 7. Confirmation codes

| CODE <sup>1</sup> | DESCRIPTION                                                                                                           |

|-------------------|-----------------------------------------------------------------------------------------------------------------------|

| 0                 | Non-broadcast packet transmitted; addressed node returned no acknowledge.                                             |

| 1                 | Broadcast packet transmitted or non-broadcast packet transmitted; addressed node returned an acknowledge complete.    |

| 2                 | Non-broadcast packet transmited; addressed node returned an acknowledge pending.                                      |

| 4                 | Retry limit exceeded; destination node hasn't accepted the non-broadcast packet within the maximum number of retries. |

| D <sub>16</sub>   | Acknowledge data error received (transaction complete).                                                               |

| E <sub>16</sub>   | Acknowledge type error received (transaction complete).                                                               |

### NOTE:

1. All other codes are reserved.

For every packet written in a transmitter queue by the CPU, there will be one confirmation written in the corresponding receiver queue by the AV layer logic.

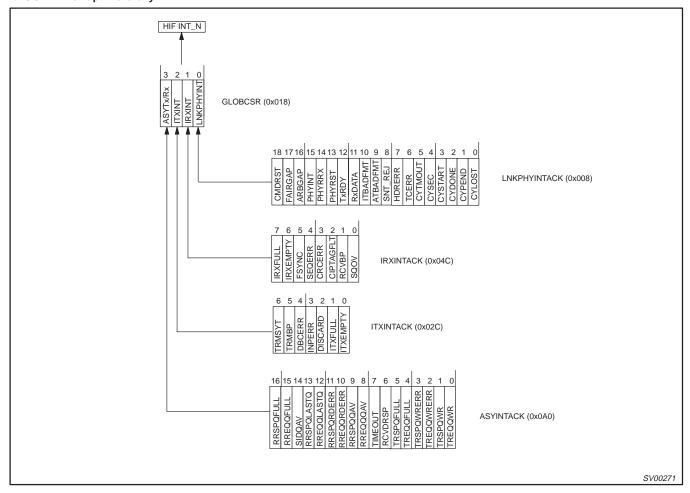

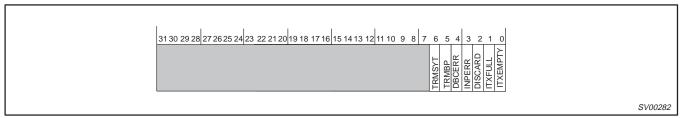

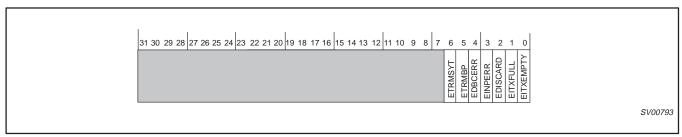

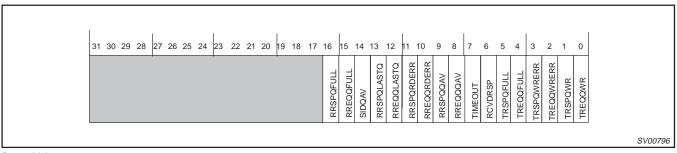

### 12.5.3 Interrupts

The PDI1394L11 provides a single interrupt line (HIF INT\_N) for connection to a host controller. Status indications from four major areas of the device are collected and ORed together to activate HIF INT\_N. Status from four major areas of the device are collected in four status registers; LNKPHYINTACK, ITXINTACK, IRXINTACK, and ASYINTACK. At this level, each individual status can be enabled to generate a chip-level interrupt by activating HIF INT\_N. To aid in determining the source of a chip-level interrupt, the major area of the device generating an interrupt is indicated in the lower 4 bits of the GLOBCSR register. These bits are non-latching Read-Only status bits and do not need to be acknowledged. To acknowledge and clear a standing interrupt, the bit in LNKPHYINTACK, ITXINTACK, IRXINTACK, or ASYINTACK causing the interrupt status has to be written to a logic '1'; Note: Writing a value of '0' to the bit has no effect.

# 1394 AV link layer controller

PDI1394L11

### 12.5.3.1 Determining and Clearing Interrupts

When responding to an interrupt event generated by the PDI1394L11, or operating in polled mode, the first register examined is the GLOBCSR register. The least significant nibble contains interrupt status bits from general sections of the device; the link layer controller, the AV transmitter, the AV receiver, and the asynchronous transceiver. The bits in GLOBCSR[3:0] are self clearing status bits. They represent the logical OR of all the enabled interrupt status bits in their section of the AV Link Layer Controller.

Once an interrupt, or status is detected in GLOBCSR, the appropriate interrupt status register needs to be read, see the Interrupt Hierarchy diagram for more detail. After all the interrupt indications are dealt with in the appropriate interrupt status register, the interrupt status indication will automatically clear in the GLOBCSR.

All interrupt status bits in the various interrupt status registers are latching unless otherwise noted.

#### 12.5.3.2 Interrupt Hierarchy

# 1394 AV link layer controller

PDI1394L11

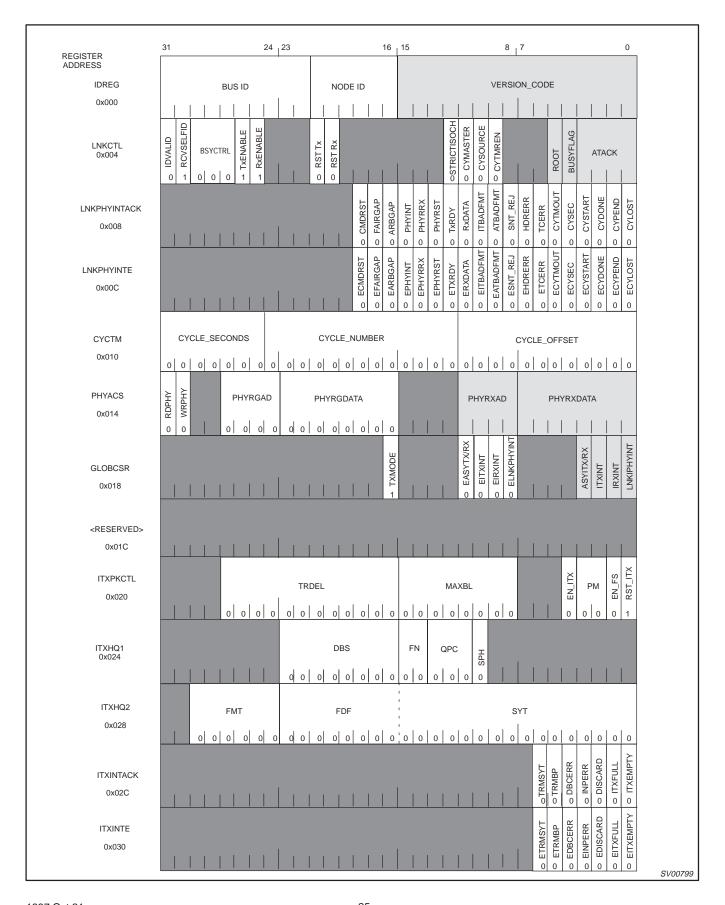

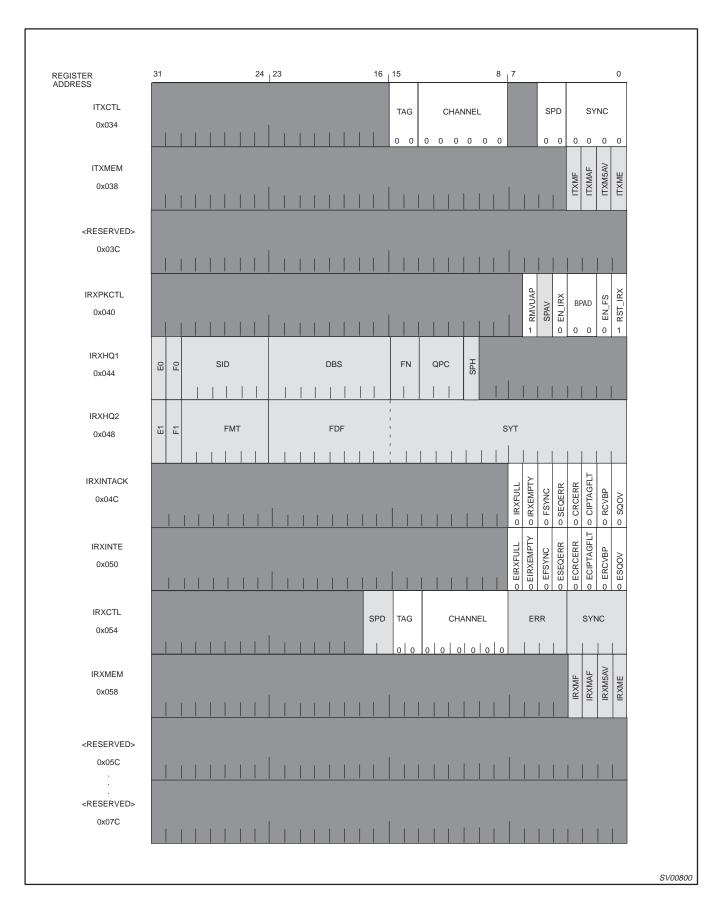

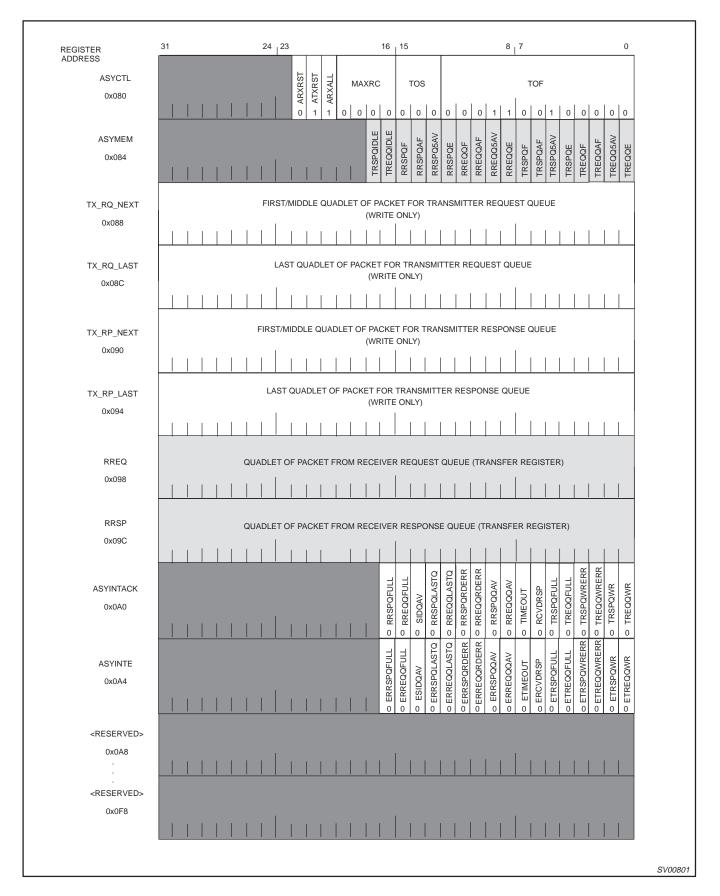

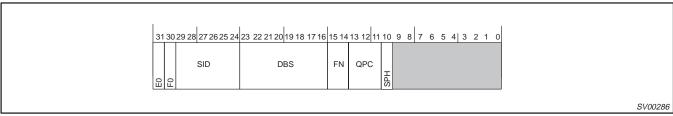

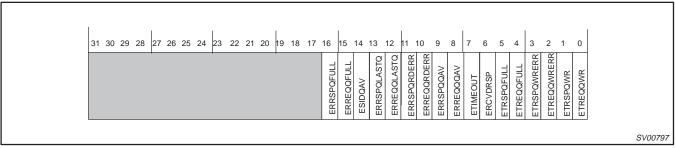

### 13.0 REGISTER MAP

Registers are 32 bits (quadlet) wide and all accesses are always done on a quadlet basis. This means that it is not possible to write just the lower 8 bits, and leave the other bits unaffected (see Section 12.3.2 for more information). The values written to undefined fields/bits are ignored and thus DON'T CARE.

A full bitmap of all registers is listed in Table 8. The meaning of shading and bit cell values is as follows:

A bit/field with no name written in it and dark shading is reserved and not used.

A bit/field with a name in it and light shading is a READ ONLY (status) bit/field.

A one bit value (0 or 1) written at the bottom of a writable (control) bit is the default value after power-on-reset.

Table 8. Full Bitmap of all Registers (consists of three tables shown on the following pages)

### PDI1394L11

### PDI1394L11

Product specification

### PDI1394L11

### 1394 AV link layer controller

PDI1394L11

### 13.1 Link Control Registers

### 13.1.1 ID Register (IDREG) - Base Address: 0x000

The ID register is automatically updated by the attached PHY with the proper Node ID after completion of the bus reset.

Reset Value 0xFFFF0002

Bit 31...22: R/W Bus ID:The 10-bit bus number that is used with the Node ID in the source address for outgoing packets and used to

accept or reject incoming packets. This field reverts to all '1's (0x3FF) upon bus reset.

Bit 21..16: R/W Node ID: Used in conjunction with Bus ID in the source address for outgoing packets and used to accept or reject

incoming packets. This register auto-updates with the node ID assigned after the 1394 bus Tree-ID sequence.

Bit 15..0: R Version Code: Version of the PDI1394L11

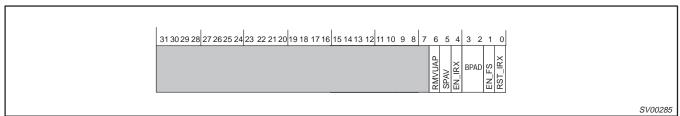

### 13.1.2 General Link Control (LNKCTL) - Base Address: 0x004

The General Link control register is used to program the Link Layer isochronous transceiver, as well as the overall link transceiver. It also provides general link status.

| 31 3 | 30 29 28 27 26 25 24 | 23 22 21 20 19 18 17 | 7 16 15 14 13 12 11 10 9 8 7          | 6 5 4            | 3 2 1 0 |   |

|------|----------------------|----------------------|---------------------------------------|------------------|---------|---|

| ALID | RXENABLE  RXENABLE   | RST Tx               | STRICTISOCH CYMASTER CYSOURCE CYTMREN | ROOT<br>BUSYFLAG | ATACK   |   |

|      |                      |                      |                                       |                  |         | ٤ |

Reset Value 0x46000000 Bit 31: ID Valid: When equal to one, the PDI1394L11 accepts the packets addressed to this node. This bit is automatically set after selfID complete and node ID is updated. Bit 30: R/W Receive Self ID: When asserted, the self-identification packets, generated by each PHY device on the bus, during bus initialization are received and placed into the asynchronous request queue as a single packet. Bit 29.27: R/W Busy Control: These bits control what busy status the chip returns to incoming packets. The field is defined below: 000 = use protocol requested by received packet (either dual phase or single phase) 001 = send busy A when it is necessary to send a busy acknowledge (testing/diagnostics) 010 = send a busy B when it is necessary to send a busy acknowledge (testing/diagnostics) 011 = use single phase retry protocol 100 = use protocol requested in packet, always send a busy ack (for all packets) 101 = busy A all incoming packets 110 = busy B all incoming packets are '1' 111 = use single phase retry protocol, always send a busy ack Bit 26: R/W Transmitter Enable: When this bit is set, the link layer transmitter will arbitrate and send packets. Bit 25: R/W Receiver Enable: When this bit is set, the link layer receiver will receive and respond to bus packets. Bit 21: R/W Reset Transmitter: When set to one, this synchronously resets the transmitter within the link layer. R/W Bit 20: Reset Receiver: When set to one, this synchronously resets the receiver within the link layer. Bit 12: R/W

Strict Isochronous: Used to accept or reject isochronous packets sent outside of specified isochronous cycles (between a Cycle Start and subaction gap). A '1' rejects packets sent outside the specified cycles, a "0" accepts isochronous packets sent outside the specified cycle.

Bit 11: R/W Cycle Master: When asserted and the PDI1394L11 is attached to the root PHY (ROOT bit = 1), and the cycle\_count

field of the cycle timer register increments, the transmitter sends a cycle-start packet. Cycle Master function will be disabled if a cycle timeout is detected (CYTMOUT bit 5 in LNKPHYINTACK). To restart the Cycle Master function in

such a case, first reset CYMASTER, then set it again.

# 1394 AV link layer controller

PDI1394L11

| Bit 10: | R/W | Cycle Source: When asserted, the cycle_count field increments and the cycle_offset field resets for each positive transition of CYCLEIN. When deasserted, the cycle count field increments when the cycle_offset field rolls over. |

|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 9:  | R/W | Cycle Timer Enable: When asserted, the cycle offset field increments.                                                                                                                                                              |

| Bit 5:  | R   | Root: Indicates this device is the root on the bus. This automatically updates after the self_ID phase.                                                                                                                            |

| Bit 4:  | R   | Busy Flag: The type of busy acknowledge which will be sent next time an acknowledge is required. 0 = Busy A, 1 = Busy B (only meaningful during a dual-phase busy/retry operation).                                                |

| Bit 30: | R   | AT acknowledge received: The last acknowledge received by the transmitter in response to a packet sent from the transmit-FIFO interface while the ATF is selected (diagnostic purposes).                                           |

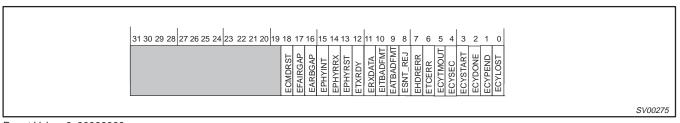

### 13.1.3 Link /Phy Interrupt Acknowledge (LNKPHYINTACK) – Base Address: 0x008

The Link/Phy Interrupt Acknowledge register indicates various status and error conditions in the Link and Phy which can be programmed to generate an interrupt. The interrupt enable register (LNKPHYINTE) is a mirror of this register. Acknowledgment of an interrupt is accomplished by writing a '1' to a bit in this register that is set. This action reset the bit indication to a '0'. Writing a '1' to a bit that is already "0" will have no effect on the register.

| CMDRST |         |

|--------|---------|

|        | SV00274 |

|          |                | SV00274                                                                                                                                                                                                                    |

|----------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset Va | lue 0x00000000 |                                                                                                                                                                                                                            |

| Bit 18:  | R/W            | Command Reset Received: A write request to RESET-START has been received.                                                                                                                                                  |

| Bit 17:  | R/W            | Fair Gap: The serial bus has been idle for a fair-gap time (called subaction gap in the IEEE 1394 specification).                                                                                                          |

| Bit 16:  | R/W            | Arbitration Reset Gap: The serial bus has been idle for an arbitration reset gap.                                                                                                                                          |

| Bit 15:  | R/W            | Phy Chip Int: The Phy chip has signaled an interrupt through the Phy interface.                                                                                                                                            |

| Bit 14:  | R/W            | Phy Register Information Received: A register has been transferred by the Physical Layer device into the Link.                                                                                                             |

| Bit 13:  | R/W            | Phy Reset Started: A Phy-layer reconfiguration has started. This interrupt clears the ID valid bit. (Called Bus Reset in the IEEE 1394 specification).                                                                     |

| Bit 12:  | R/W            | Transmitter Ready: The transmitter is idle and ready.                                                                                                                                                                      |

| Bit 11:  | R/W            | Receiver has Data: The receiver has confirmed data to the receiver response/request FIFO. Used for diagnostic purposes only.                                                                                               |

| Bit 10:  | R/W            | Isochronous Transmitter is Stuck: The transmitter has detected invalid data at the transmit-FIFO interface when the ITF is selected.                                                                                       |

| Bit 9:   | R/W            | Asynchronous Transmitter is Stuck: The transmitter expected start of new async packet in queue, but found other data (out of sync with user). Reset to clear.                                                              |

| Bit 8:   | R/W            | Busy Acknowledge Sent by Receiver: The receiver was forced to send a busy acknowledge to a packet addressed to this node because the receiver response/request FIFO overflowed.                                            |

| Bit 7:   | R/W            | Header Error: The receiver detected a header CRC error on an incoming packet that may have been addressed to this node.                                                                                                    |

| Bit 6:   | R/W            | Transaction Code Error: The transmitter detected an invalid transaction code in the data at the transmit FIFO interface.                                                                                                   |

| Bit 5:   | R/W            | Cycle Timed Out. ISOCH cycle lasted more than 125µs from Cycle-Start to Fair Gap: Disables cycle master function                                                                                                           |

| Bit 4:   | R/W            | Cycle Second incremented: The cycle second field in the cycle-timer register incremented. This occurs approximately every second when the cycle timer is enabled.                                                          |

| Bit 3:   | R/W            | Cycle Started: The transmitter has sent or the receiver has received a cycle start packet.                                                                                                                                 |

| Bit 2:   | R/W            | Cycle Done: A fair gap has been detected on the bus after the transmission or reception of a cycle start packet. This indicates that the isochronous cycle is over; Note: Writing a value of '0' to the bit has no effect. |

| Bit 1:   | R/W            | Cycle Pending: Cycle pending is asserted when cycle timer offset is set to zero (rolled over or reset) and stays asserted until the isochronous cycle has ended.                                                           |

| Bit 0:   | R/W            | Cycle Lost: The cycle timer has rolled over twice without the reception of a cycle start packet. This only occurs when cycle master is not asserted.                                                                       |

### 1394 AV link layer controller

PDI1394L11

### 13.1.4 Link / Phy Interrupt Enable (LNKPHYINTE) - Base Address: 0x00C

This register is a mirror of the Link/Phy Interrupt Acknowledge (LNKPHYINTACK) register. Enabling an interrupt is accomplished by writing a '1' to the bit corresponding to the interrupt desired.

This register enables the interrupts described in the Link /Phy Interrupt Acknowledge register (LNKPHYINTACK) description. A one in any of the bits enables that function to create an interrupt. A zero disables the interrupt, however the status is readable in the Link /Phy Interrupt Acknowledge register.

Reset Value 0x00000000

Bits 18..0 are interrupt enable bits for the Link/Phy Interrupt Acknowledge (LNKPHYINTACK).

### 13.1.5 Cycle Timer Register (CYCTM) - Base Address: 0x010